# MicroSys MICROWARE® OS-9 EtherCAT Master Stack

Deterministic - Efficient - Scalable - Fast Booting

#### Microware OS-9 in short

Microware OS-9 is a full-featured operating system framework, including the OS kernel, kernel services and industry-standard APIs, middleware and a complete IDE based development framework. The OS-9's compact, high-performance, multi-user, multi-tasking real-time kernel is a proven foundation for time-to-revenue success. OS-9 supports Freescales Power Architecture, Intel Platforms, ARM-, SHx, MIPS and others. It offers:

- Hard Real-Time Performance

- Small Footprint

- Scalable Modular Architecture

- Power Management / Efficiency

- Reliable, Safe and Secure

- Multi-Core and Virtualization

- Extensive Services and Middleware

- Native Development Framework

# EtherCAT Master Stack for OS-9 in brief

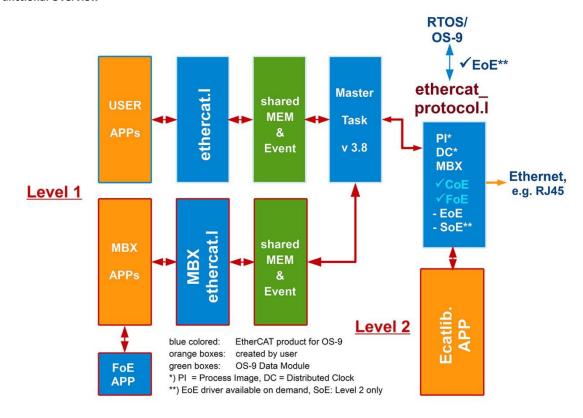

The EtherCAT Master Stack for OS-9 is based on the Beckhoff Master Sample Code and optimized to meet the requirements of hard real-time operation under the RTOS OS-9. The cycle time can go down to 50µs depending on CPU-performance, number of slaves and data size. EtherCAT Master is ENI based, thus accepts any configuration created in accordance with EtherCAT specifications. EtherCAT Master has a modular architecture and consists of the following layers to adapt the programmers need to create user applications on different convenience and complexity levels.

#### Level One, the EtherCAT Master Task

The user application coexists to the EtherCAT master task. The user application communicates event synchronized over shared memory with the EtherCAT master task. The access by the user application to the EtherCAT field I/O is based on configured symbolic field variable names. The configuration is done by an EtherCAT configuration tool or by the application writer himself. Level one is today's preferred model of usage.

<u>Please note!</u> Not all but most level two features are available in level one.

# Level Two, the EtherCAT Library

The EtherCAT Mastertask itself uses the EtherCAT library for all communication purposes. Actually from the point of view of the EtherCAT library the EtherCAT master task is just an "ordinary" user application. So for advanced programmers familiar to the EtherCAT communication standards can use the library directly, especially if the complete feature set is intended to be used directly on the application level. Then the user application is direct plugged in to the EtherCAT library bypassing all intermediate levels.

#### **Functional Overview Level One and Two: EtherCAT Library**

The EtherCAT Library (ethercat\_protocol.l) provides the following functionality (Level one functions are indicated by a \*sign and level two by a #sign!):

#### Process Image (\*)

- No file systems needed

- Cyclic Data Exchange (periodic frames down to 50μs, depends on hardware performance, numbers of slaves and data size

- Acyclic Process Data Exchange (PDO in SDO)

- Different Process Image Update Cycle Times (as specified in the XML configuration file)

- Process Image memory may be provided externally by application e.g. EtherCAT master task (\*, #)

- Large Process Images (exceeding Ethernet frame length) (\*, #)

#### Master Configuration (\*, #)

- XML Schema (Conforming ENI Specification)

- No ESI (EtherCAT Slave Information File) upload from EEPROM

#### Mailbox Communication (MBX) (\*, #)

- Application Interface installable User-Callbacks

- Mailbox Protocols

- CAN application protocol over EtherCAT (CoE)

- Application uses standard Mailbox Communication Interface

- SDO upload, SDO download, SDO information service, Emergency Request (library only)

### Ethernet over EtherCAT (EoE) (\*, #)

OS-9 Driver available on demand

Servo drive profile according to IEC 61491 over EtherCAT (SoE) (Level 2 only)

#### File Access over EtherCAT (FoE) (\*, #)

Firmeware up and download

# Distributed Clocks (DC) (\*,#)

- Distributed Clocks of slaves synchronized by master

- Offset and delay compensation

### **Supported CPU-architectures to date:**

- Freescales Power Architecture, QorlQ, i.MX, Layerscape

- Intel Architecture

- ARM

#### **Functional Overview**

### Who is standing behind Microware OS-9?

Since February 2013 Microware OS-9 is owned by a partnership of three companies, MicroSys, Freestation (Japan) and RTSI (USA).

MicroSys in Sauerlach near Munich takes care of customers in Europe, provides technical support and actively continues the development on OS-9. Recent enhancements already provide support for ARM Cortex A8 and A9 cores with Freescale's latest i.MX5x and i.MX6 CPUs.

MicroSys

Electronics GmbH

Tel: +49 (0)8104 801-0

Muehlweg 1

Hotline: +49 (0)8104 801-130

D-82054 Sauerlach

Fax: +49 (0)8104 801-110

Germany

www.MicroSys.de

Email: info@microsys.de