# miriac MPX-S32G274A

**User Manual (HW Revision 2)**

**V2.3**

# **Table of Contents**

| 1      | General Notes                          | 3   | 4.12.8  | I2C                                     | 36 |

|--------|----------------------------------------|-----|---------|-----------------------------------------|----|

| 1.1    | Warranty                               | 3   | 4.12.9  | QSPI (Flash)                            | 38 |

| 1.2    | Links                                  | 3   | 4.12.10 | SPI                                     | 39 |

| 1.3    | Liability                              | 3   | 4.12.11 | UART                                    | 39 |

| 1.4    | Offer to Provide Source Code of Certai | in  | 4.12.12 | LIN                                     | 39 |

|        | Software                               | 4   | 4.12.13 | FlexRay                                 | 39 |

| 1.5    | Symbols, Conventions and Abbreviation  | ns5 | 4.12.14 | SDHC                                    | 40 |

| 1.5.1  | Symbols                                | 5   | 4.12.15 | SerDes                                  | 41 |

| 1.5.2  | Conventions                            | 5   | 5       | Mechanical Description                  | 43 |

| 1.6    | Safety and Handling Precautions        | 6   | 5.1     | Edge Connector                          | 43 |

| 2      | Short Description                      | 7   | 5.2     | Previous Numbering Scheme               | 44 |

| 3      | System Description                     | 8   | 5.3     | Current Numbering Scheme                | 44 |

| 3.1    | Block Diagram                          | 8   | 5.4     | Pin-Layout                              | 45 |

| 3.2    | System Components                      | 8   | 5.5     | Mounting/Unmounting                     | 47 |

| 3.3    | Ordering Information                   | 8   | 5.6     | Board Outline                           | 48 |

| 3.4    | Power Consumption                      | 9   | 5.7     | Height                                  | 49 |

| 3.5    | Cooling                                | 9   | 5.8     | Thickness                               | 49 |

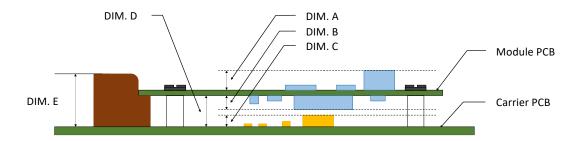

| 4      | Technical Description                  | 11  | 5.9     | Component Layout - Top Side             | 50 |

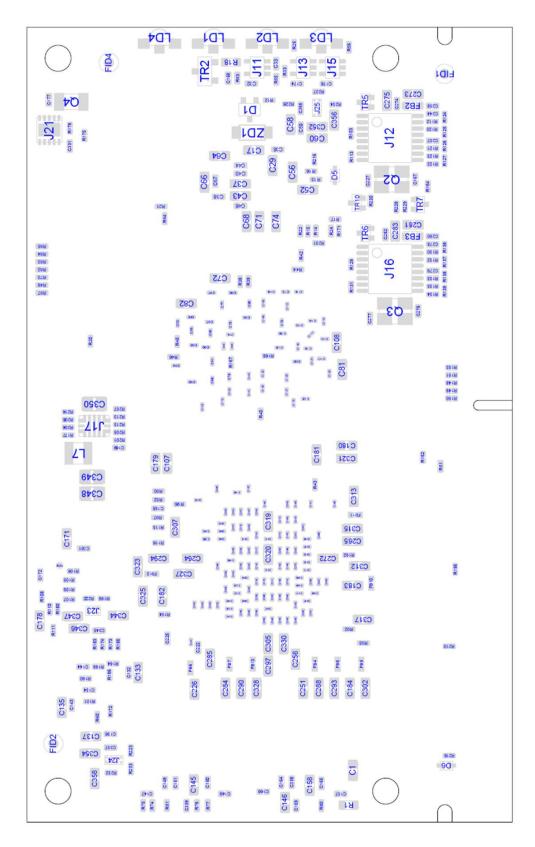

| 4.1    | Pinouts                                | 11  | 5.10    | Component Layout – Bottom Side          | 52 |

| 4.1.1  | Module Connector – Top Pins            | 11  | 6       | Software                                | 54 |

| 4.1.2  | Module Connector – Bottom Pins         | 16  | 6.1     | U-Boot                                  | 54 |

| 4.2    | Power Structure                        | 21  | 6.2     | Operating System                        | 54 |

| 4.3    | Reset Structure                        | 22  | 7       | Safety Requirements And Protective      |    |

| 4.4    | Clock Structure                        | 23  |         | Regulations                             | 55 |

| 4.5    | Boot Mode Configuration                | 26  | 7.1     | EMC                                     | 55 |

| 4.6    | LEDs                                   | 27  | 7.2     | ESD                                     | 55 |

| 4.7    | RTC                                    | 28  | 7.3     | Reliability                             | 55 |

| 4.8    | Temperature sensor                     | 29  | 7.4     | Climatic conditions                     | 56 |

| 4.9    | GPIO Expander                          | 30  | 7.5     | RoHS                                    | 56 |

| 4.10   | Serial Boot EEPROM (RCON)              | 31  | 8       | General notes                           | 57 |

| 4.11   | Electronic DIP Switch                  | 32  | 9       | History                                 | 58 |

| 4.12   | Interface Description                  | 34  | 10      | Appendix                                | 59 |

| 4.12.1 | Definition of "Primary Interfaces"     | 34  | 10.1    | Acronyms                                | 59 |

| 4.12.2 | JTAG                                   | 34  | 10.2    | Table of Figures                        | 60 |

| 4.12.3 | AURORA                                 | 34  | 10.3    | Table of Tables                         | 61 |

| 4.12.4 | ADC                                    | 34  | 10.4    | Pin Definitions – Top                   | 62 |

| 4.12.5 | CAN                                    | 35  | 10.5    | Pin Definitions – Bottom                | 69 |

| 4.12.6 | RGMII                                  | 35  | 10.6    | Pins not available for pin multiplexing | 76 |

| 4.12.7 | ULPI (USB)                             | 36  |         |                                         |    |

# 1 General Notes

#### Copyright MicroSys Electronics GmbH, January 2020

All rights reserved. All rights in any information which appears in this document belong to MicroSys Electronics GmbH or our licensors. You may copy the information in this manual for your personal, non-commercial use.

Copyrighted products are not explicitly indicated in this manual. The absence of the copyright (©) and trademark (TM or ®) symbols does not imply that a product is not protected. Additionally, registered patents and trademarks are similarly not expressly indicated in this manual.

## 1.1 Warranty

To the extent permissible by applicable law all information in this document is provided without warranty of any kind, whether expressed or implied, including but not limited to any implied warranty of satisfactory quality or fitness for a particular purpose, or of non-infringement of any third party's rights. We try to keep this document accurate and up to date but we do not make any warranty or representation about such matters. In particular we assume no liability or responsibility for any errors or omissions in this document.

MicroSys Electronics GmbH neither gives any guarantee nor accepts any liability whatsoever for consequential damages resulting from the use of this manual or its associated product.

MicroSys Electronics GmbH further reserves the right to alter the layout and/or design of the hardware without prior notification and accepts no liability for doing so.

### 1.2 Links

We make no warranty about any other sites that are linked to or from this document, whether we authorize such links or not.

## 1.3 Liability

To the extent permissible by applicable law, in no circumstance, including (but not limited to) negligence, shall we be liable for your reliance on any information in this document, nor shall we be liable for any direct, incidental, special, consequential, indirect or punitive damages nor any loss of profit that result from the use of, or the inability to use, this document or any material on any site linked to this document even if we have been advised of the possibility of such damage. In no event shall our liability to you for all damages, losses and causes of action whatsoever, whether in contract, tort (including but not limited to negligence) or otherwise exceed the amount, if any, paid by you to us for gaining access to this document.

MicroSys Electronics GmbH Muehlweg 1 82054 Sauerlach Germany

Phone: +49 8104 801-0 Fax: +49 8104 801-110

# 1.4 Offer to Provide Source Code of Certain Software

This product contains copyrighted software that is licensed under the General Public License ("GPL") and under the Lesser General Public License Version ("LGPL"). The GPL and LGPL licensed code in this product is distributed without any warranty. Copies of these licenses are included in this product.

You may obtain the complete corresponding source code (as defined in the GPL) for the GPL Software, and/or the complete corresponding source code of the LGPL Software (with the complete machine-readable "work that uses the Library") for a period of three years after our last shipment of the product including the GPL Software and/or LGPL Software, which will be no earlier than December 1, 2010, for the cost of reproduction and shipment, which is dependent on the preferred carrier and the location where you want to have it shipped to, by sending a request to:

MicroSys Electronics GmbH Muehlweg 1 82054 Sauerlach Germany

In your request please provide the product name and version for which you wish to obtain the corresponding source code and your contact details so that we can coordinate the terms and cost of shipment with you.

The source code will be distributed WITHOUT ANY WARRANTY and licensed under the same license as the corresponding binary/object code.

This offer is valid to anyone in receipt of this information.

MicroSys Electronics GmbH is eager to duly provide complete source code as required under various Free Open Source Software licenses. If however you encounter any problems in obtaining the full corresponding source code we would be much obliged if you give us a notification to the email address gpl@microsys.de, stating the product and describing the problem (please do NOT send large attachments such as source code archives etc. to this email address)

# 1.5 Symbols, Conventions and Abbreviations

### 1.5.1 Symbols

Throughout this document, the following symbols will be used:

Information marked with this symbol MUST be obeyed to avoid the risk of severe injury, health danger, or major destruction of the unit and its environment

Information marked with this symbol MUST be obeyed to avoid the risk of possible injury, permanent damage or malfunction of the unit.

Information marked with this symbol gives important hints upon details of this manual, or in order to get the best use out of the product and its features.

Table 1 Symbols

#### 1.5.2 Conventions

| Symbol            | Explanation                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------|

| # / xxx_B         | denotes a low active signal                                                                              |

| <b>←</b>          | denotes the signal flow in the direction shown                                                           |

| $\rightarrow$     | denotes the signal flow in the direction shown                                                           |

| $\leftrightarrow$ | denotes the signal flow in both directions                                                               |

| $\rightarrow$     | denotes the signal flow in the direction shown with additional logic / additional ICs in the signal path |

| I/O / INOUT       | denotes a bidirectional pin                                                                              |

| Input             | denotes an input pin                                                                                     |

| Output            | denotes an output pin                                                                                    |

| matched           | denotes the according signal to be routed impedance controlled and length matched                        |

| Pin 1             | refers to the numeric pin of a component package                                                         |

| Pin a1            | refers to the array position of a pin within a component package                                         |

| xxx- / xxx_N      | denotes the negative signal of a differential pair                                                       |

| xxx+ / xxx_P      | denotes the positive signal of a differential pair                                                       |

| XXX               | denotes an optional not mounted or fitted part                                                           |

Table 2 Conventions

# 1.6 Safety and Handling Precautions

DO NOT exceed the rated maximum values for the power supply! This may result in severe permanent damage to the unit, as well as possible serious injury.

ALWAYS keep the unit dry, clean and free of foreign objects. Otherwise, irreparable damage may occur.

Parts of the unit may become hot during operation. Take care not to touch any parts of the circuitry during operation to avoid burns and operate the unit in a well-ventilated location. Provide an appropriate cooling solution as required.

Electrostatic discharge (ESD) can damage the unit. Always take the necessary ESD precautions.

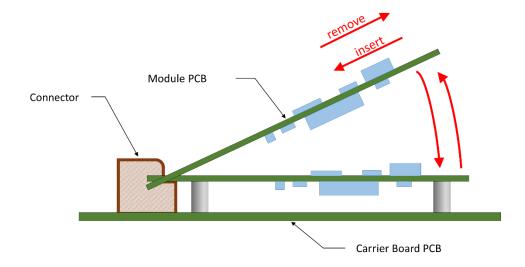

Many pins on the module connector are directly connected to the SOC or other ESD sensitive devices. Make or break ANY connection ONLY while the unit is switched OFF.

Otherwise, permanent damage to the unit may occur, which is not covered by warranty.

There is no separate SHIELD connection.

The module's mounting holes are <u>not</u> connected to GND Take this into account when handling and mounting the unit.

Table 3 Safety and Handling Precautions

# 2 Short Description

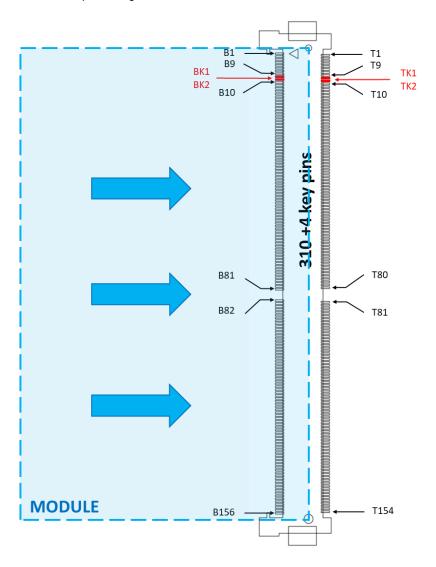

The miriac MPX-S32G274A is a member of the MPX module family based on NXP's S32G274A network processor (SoC).

MicroSys Electronics GmbH offers a Development Kit which uses the key features of the module. The customer can:

- ...test the operation of the MPX-S32G274A module

- ...evaluate the main interfaces of the S32G274A SoC

- ...test the provided software

- ...start developing

# 3 System Description

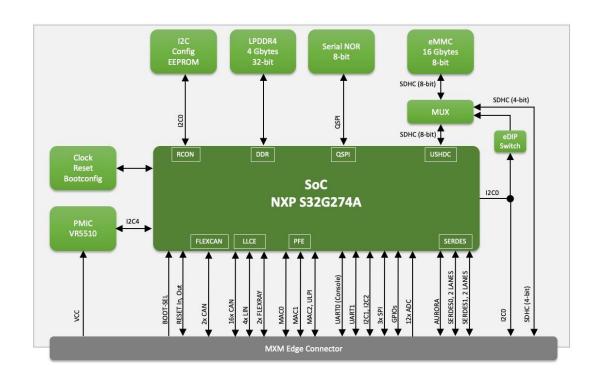

# 3.1 Block Diagram

Figure 3-1 Block Diagram

# 3.2 System Components

- S32G274A SoC (4x Arm Cortex-A53 plus triple Cortex-M7 lockstep cores)

- 4GB LPDDR4 SDRAM

- Serial NOR flash as boot or storage device

- 16GB eMMC flash as boot or storage device

- Clock generators for SOC and interface clocks

- I<sup>2</sup>C EEPROM

- I<sup>2</sup>C temperature sensor

- I<sup>2</sup>C RTC

- Voltage regulators for onboard voltages

## 3.3 Ordering Information

Ordering information can be found on the following website

miriac MPX-S32G274A

or contact your local sales representative.

## 3.4 Power Consumption

The MPX-S32G274A is supplied by a single input power rail.

The typical power consumption values for the module are determined on a CRX-S32G carrier running U-Boot (idle) at room temperature with heatsink:

- S32G274A

- Cortex-A53 core frequency 1000 MHz

- 400 MHz bus clock

- 4 GBytes of LPDDR4 memory + ECC (1600 MHz)

| Nominal Input<br>Power | Power Dissipation |

|------------------------|-------------------|

| 9V                     | 2.88 W            |

| 12V                    | 2.95 W            |

| 18V                    | 3.06 W            |

| 24V                    | 3.36 W            |

| 30V                    | 3.49 W            |

Table 4 Typical power consumption at U-Boot prompt

The typical power consumption values for the module over junction temperature are determined on a CRX-S32G carrier running Linux based on BSP 31. Input voltage 12V with 4 times RJ45 1G Ethernet connected as well as console over USB.

Linux Stress: stressapptest (<a href="https://github.com/stressapptest/stressapptest">https://github.com/stressapptest/stressapptest</a>) (start parameters: -W -s 60, all cores)

Linux Idle: command prompt

| T <sub>i</sub> [°C] from internal probe | Power dissipation idle [W] | Power dissipation stress [W] |

|-----------------------------------------|----------------------------|------------------------------|

| -25                                     | 5,6                        | 6,7                          |

| -20                                     | 5,6                        | 6,6                          |

| 0                                       | 5,4                        | 6,5                          |

| 15                                      | 5,5                        | 6,6                          |

| 25                                      | 5,4                        | 6,6                          |

| 50                                      | 5,6                        | 6,7                          |

Table 5 Typical power consumption running module with Linux

## 3.5 Cooling

In chapter 3.4 the typical power consumption of the MPX-S32G274A module was specified. With this information a cooling method needs to be designed which considers the final use case. If desired, MicroSys Electronics GmbH can support

you with your cooling concept. Please ask your sales representative or send an email inquiry to <a href="mailto:support@microsys.de">support@microsys.de</a>.

| Component | Temperature<br>(max.)   | Power Dissipation (max.) |

|-----------|-------------------------|--------------------------|

| SoC       | $T_J = 125^{\circ} C$   | 5.1 W                    |

| LPDDR4    | T <sub>C</sub> = 95° C  | 0.4 W                    |

| eMMC      | T <sub>C</sub> = 115° C | 0.62 W                   |

Table 6 Maximum junction/case temperatures

Do not run the module without a heatsink or appropriate cooling concept

# 4 Technical Description

## 4.1 Pinouts

The signal direction is from the module's view. For example, PCIE0\_TX0\_N, pin T90, is an output from the module and an input to peripheral devices on the carrier.

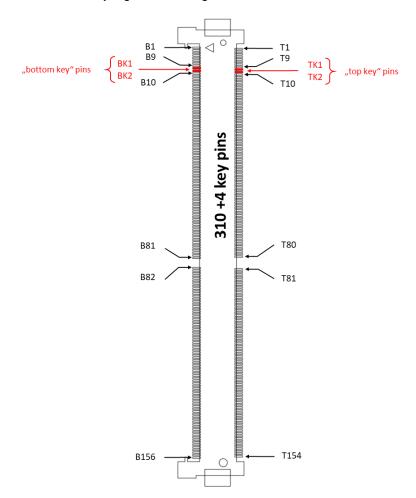

The following table gives an overview of the 314 pins of the module's edge finger. For a detailed connector description see chapter 5.1. The pins will be described in chapter 4.10 and the following sections.

The signal names in the following two tables do not show all available options for each pin. Pin multiplexing can only be implemented in combination with the vendor's datasheet.

### 4.1.1 Module Connector – Top Pins

| Pin | Pin Name /<br>Primary Function | Alternate<br>Functions | GPIO?        |

|-----|--------------------------------|------------------------|--------------|

| T1  | GND                            |                        |              |

| T2  | SD_CLK                         |                        | $\checkmark$ |

| Т3  | GND                            |                        |              |

| T4  | SD_CMD                         |                        | $\checkmark$ |

| T5  | GND                            |                        |              |

| Т6  | SD_D0                          |                        | $\checkmark$ |

| T7  | SD_D1                          |                        | $\checkmark$ |

| Т8  | SD_D2                          |                        | $\checkmark$ |

| Т9  | SD_D3                          |                        | $\checkmark$ |

| TK1 | VCC_SDHC_1V8/3V3               |                        |              |

| TK2 | PMIC_FCCU1_OUT                 |                        |              |

| T10 | GND                            |                        |              |

| T11 | GND                            |                        |              |

| T12 | RGMII2_MDC/DSPI0_CS7           | $\checkmark$           | $\checkmark$ |

| T13 | RGMII2_MDIO                    | $\checkmark$           | $\checkmark$ |

| T14 | GND                            |                        |              |

| T15 | RGMII2_RXD3/USB_D7             | $\checkmark$           | $\checkmark$ |

| T16 | RGMII2_RXD2/USB_D6             | $\checkmark$           | $\checkmark$ |

| T17 | RGMII2_RXD1/USB_D5             | $\checkmark$           | $\checkmark$ |

| T18 | RGMII2_RXD0/USB_D4             | $\checkmark$           | $\checkmark$ |

| T19 | GND                            |                        |              |

| T20 | RGMII2_RXDV/USB_D3             | $\checkmark$           | $\checkmark$ |

11/77

| Pin | Pin Name /<br>Primary Function | Alternate<br>Functions | GPIO?        |

|-----|--------------------------------|------------------------|--------------|

| T21 | RGMII2_RX_CLK/USB_D2           | $\checkmark$           | $\checkmark$ |

| T22 | GND                            |                        |              |

| T23 | RGMII2_TXD3/USB_D1             | $\checkmark$           | $\checkmark$ |

| T24 | RGMII2_TXD2/USB_D0             | $\checkmark$           | $\checkmark$ |

| T25 | RGMII2_TXD1/USB_NXT            | $\checkmark$           | $\checkmark$ |

| T26 | RGMII2_TXD0/USB_STP            | $\checkmark$           | $\checkmark$ |

| T27 | GND                            |                        |              |

| T28 | RGMII2_TX_EN/USB_DIR           | $\checkmark$           | $\checkmark$ |

| T29 | RGMII2_TX_CLK/USB_CLK          | $\checkmark$           | $\checkmark$ |

| T30 | GND                            |                        |              |

| T31 | RGMII1_MDC                     | $\checkmark$           | $\checkmark$ |

| T32 | RGMII1_MDIO                    | $\checkmark$           | $\checkmark$ |

| T33 | GND                            |                        |              |

| T34 | RGMII1_RXD3                    | $\checkmark$           | $\checkmark$ |

| T35 | RGMII1_RXD2                    | $\checkmark$           | $\checkmark$ |

| T36 | RGMII1_RXD1                    | $\checkmark$           | $\checkmark$ |

| T37 | RGMII1_RXD0                    | $\checkmark$           | $\checkmark$ |

| T38 | GND                            |                        |              |

| T39 | RGMII1_RXDV                    | $\checkmark$           | $\checkmark$ |

| T40 | RGMII1_RX_CLK                  | $\checkmark$           | $\checkmark$ |

| T41 | GND                            |                        |              |

| T42 | RGMII1_TXD3                    | $\checkmark$           | $\checkmark$ |

| T43 | RGMII1_TXD2                    | $\checkmark$           | $\checkmark$ |

| T44 | RGMII1_TXD1                    | $\checkmark$           | $\checkmark$ |

| T45 | RGMII1_TXD0                    | $\checkmark$           | $\checkmark$ |

| T46 | GND                            |                        |              |

| T47 | RGMII1_TX_EN                   | $\checkmark$           | $\checkmark$ |

| T48 | RGMII1_TX_CLK                  | $\checkmark$           | $\checkmark$ |

| T49 | GND                            |                        |              |

| T50 | RGMII0_MDC                     | $\checkmark$           | $\checkmark$ |

| T51 | RGMII0_MDIO                    | $\checkmark$           | $\checkmark$ |

| T52 | GND                            |                        |              |

| T53 | RGMII0_RXD3                    | $\checkmark$           | $\checkmark$ |

| T54 | RGMII0_RXD2                    | $\checkmark$           | $\checkmark$ |

| T55 | RGMII0_RXD1                    | $\checkmark$           | $\checkmark$ |

| T56 | RGMII0_RXD0                    | $\checkmark$           | $\checkmark$ |

|     | Primary Function | Functions    | GPIO?        |

|-----|------------------|--------------|--------------|

| T57 | GND              |              |              |

| T58 | RGMII0_RXDV      | $\checkmark$ | $\checkmark$ |

| T59 | RGMII0_RX_CLK    | $\checkmark$ | $\checkmark$ |

| T60 | GND              |              |              |

| T61 | RGMII0_TXD3      | $\checkmark$ | $\checkmark$ |

| T62 | RGMII0_TXD2      | $\checkmark$ | $\checkmark$ |

| T63 | RGMII0_TXD1      | $\checkmark$ | $\checkmark$ |

| T64 | RGMII0_TXD0      | $\checkmark$ | $\checkmark$ |

| T65 | GND              |              |              |

| T66 | RGMII0_TX_EN     | $\checkmark$ | $\checkmark$ |

| T67 | RGMII0_TX_CLK    | $\checkmark$ | $\checkmark$ |

| T68 | GND              |              |              |

| T69 | PCIE1_RX0_N      |              |              |

| T70 | PCIE1_RX0_P      |              |              |

| T71 | GND              |              |              |

| T72 | PCIE1_RX1_N      |              |              |

| T73 | PCIE1_RX1_P      |              |              |

| T74 | GND              |              |              |

| T75 | PCIE0_RX0_N      |              |              |

| T76 | PCIE0_RX0_P      |              |              |

| T77 | GND              |              |              |

| T78 | PCIE0_RX1_N      |              |              |

| T79 | PCIE0_RX1_P      |              |              |

| T80 | GND              |              |              |

| T81 | CLK_OUT_N        |              |              |

| T82 | CLK_OUT_P        |              |              |

| T83 | GND              |              |              |

| T84 | PCIE1_TX0_N      |              |              |

| T85 | PCIE1_TX0_P      |              |              |

| T86 | GND              |              |              |

| T87 | PCIE1_TX1_N      |              |              |

| T88 | PCIE1_TX1_P      |              |              |

| T89 | GND              |              |              |

| T90 | PCIE0_TX0_N      |              |              |

| T91 | PCIE0_TX0_P      |              |              |

| T92 | GND              |              |              |

| Pin  | Pin Name /<br>Primary Function | Alternate<br>Functions | GPIO?        |

|------|--------------------------------|------------------------|--------------|

| T93  | PCIE0_TX1_N                    |                        |              |

| T94  | PCIE0_TX1_P                    |                        |              |

| T95  | GND                            |                        |              |

| T96  | AUR_CLK_N                      |                        |              |

| T97  | AUR_CLK_P                      |                        |              |

| T98  | GND                            |                        |              |

| T99  | AUR_TX2_N                      |                        |              |

| T100 | AUR_TX2_P                      |                        |              |

| T101 | GND                            |                        |              |

| T102 | AUR_TX0_N                      |                        |              |

| T103 | AUR_TX0_P                      |                        |              |

| T104 | GND                            |                        |              |

| T105 | AUR_TX1_N                      |                        |              |

| T106 | AUR_TX1_P                      |                        |              |

| T107 | GND                            |                        |              |

| T108 | AUR_TX3_N                      |                        |              |

| T109 | AUR_TX3_P                      |                        |              |

| T110 | GND                            |                        |              |

| T111 | PB02                           | $\checkmark$           | $\checkmark$ |

| T112 | PB07                           | $\checkmark$           | $\checkmark$ |

| T113 | PB08                           | $\checkmark$           | $\checkmark$ |

| T114 | PB15                           | $\checkmark$           | $\checkmark$ |

| T115 | PC00                           | $\checkmark$           | $\checkmark$ |

| T116 | GND                            |                        |              |

| T117 | +VREF1                         |                        |              |

| T118 | +VREF2                         |                        |              |

| T119 | +VREF3                         |                        |              |

| T120 | +VREF4                         |                        |              |

| T121 | GND                            |                        |              |

| T122 | PCIE0_CLKIN_N                  |                        |              |

| T123 | PCIE0_CLKIN_P                  |                        |              |

| T124 | GND                            |                        |              |

| T125 | NMI                            |                        |              |

| T126 | PMIC_RST#                      |                        |              |

| T127 | RSTIN#                         |                        |              |

| T128 | RST#                           |                        |              |

| Pin  | Pin Name /<br>Primary Function | Alternate<br>Functions | GPIO? |

|------|--------------------------------|------------------------|-------|

| T129 | GND                            |                        |       |

| T130 | SEL_CLK_RC/EP#                 |                        |       |

| T131 | RCW_SEL#                       |                        |       |

| T132 | MUX_SEL#                       |                        |       |

| T133 | VCC_RTC                        |                        |       |

| T134 | +3V3_EXT                       |                        |       |

| T135 | I2C_SCL_PROG                   |                        |       |

| T136 | I2C_SDA_PROG                   |                        |       |

| T137 | GND                            |                        |       |

| T138 | GND                            |                        |       |

| T139 | GND                            |                        |       |

| T140 | GND                            |                        |       |

| T141 | GND                            |                        |       |

| T142 | GND                            |                        |       |

| T143 | GND                            |                        |       |

| T144 | GND                            |                        |       |

| T145 | GND                            |                        |       |

| T146 | +VIN                           |                        |       |

| T147 | +VIN                           |                        |       |

| T148 | +VIN                           |                        |       |

| T149 | +VIN                           |                        |       |

| T150 | +VIN                           |                        |       |

| T151 | +VIN                           |                        |       |

| T152 | +VIN                           |                        |       |

| T153 | +VIN                           |                        |       |

| T154 | +VIN                           |                        |       |

Table 7 Module connector: top pins

## 4.1.2 Module Connector – Bottom Pins

| Pin | Pin Name /<br>Primary Function | Alternate<br>Functions | GPIO?        |

|-----|--------------------------------|------------------------|--------------|

| B1  | ADC_CH_11                      |                        |              |

| B2  | ADC_CH_10                      |                        |              |

| В3  | GND                            |                        |              |

| B4  | ADC_CH_09                      |                        |              |

| B5  | ADC_CH_08                      |                        |              |

| B6  | GND                            |                        |              |

| B7  | ADC_CH_07                      |                        |              |

| B8  | ADC_CH_06                      |                        |              |

| В9  | GND                            |                        |              |

| BK1 | PMIC_STBY#                     |                        |              |

| BK2 | PMIC_VDD_OK                    |                        |              |

| B10 | ADC_CH_05                      |                        |              |

| B11 | ADC_CH_04                      |                        |              |

| B12 | GND                            |                        |              |

| B13 | ADC_CH_03                      |                        |              |

| B14 | ADC_CH_02                      |                        |              |

| B15 | GND                            |                        |              |

| B16 | ADC_CH_01                      |                        |              |

| B17 | ADC_CH_00                      |                        |              |

| B18 | GND                            |                        |              |

| B19 | CAN00_RX                       |                        | √(INPUT)     |

| B20 | CAN00_TX                       |                        | $\checkmark$ |

| B21 | GND                            |                        |              |

| B22 | CAN01_RX                       |                        | √(INPUT)     |

| B23 | CAN01_TX                       |                        | $\checkmark$ |

| B24 | GND                            |                        |              |

| B25 | CAN02_RX                       |                        | √(INPUT)     |

| B26 | CAN02_TX                       |                        | $\checkmark$ |

| B27 | GND                            |                        |              |

| B28 | CAN03_RX                       |                        | √(INPUT)     |

| B29 | CAN03_TX                       |                        | $\checkmark$ |

| B30 | GND                            |                        |              |

| B31 | CAN04_RX                       | $\checkmark$           | √(INPUT)     |

| B32 | CAN04_TX                       | ✓                      | $\checkmark$ |

| Pin | Pin Name /<br>Primary Function | Alternate<br>Functions | GPIO?        |

|-----|--------------------------------|------------------------|--------------|

| B33 | GND                            |                        |              |

| B34 | CAN05_RX                       | $\checkmark$           | √(INPUT)     |

| B35 | CAN05_TX                       | $\checkmark$           | $\checkmark$ |

| B36 | GND                            |                        |              |

| B37 | CAN06_RX                       | $\checkmark$           | √(INPUT)     |

| B38 | CAN06_TX                       | $\checkmark$           | $\checkmark$ |

| B39 | GND                            |                        |              |

| B40 | CAN07_RX                       | $\checkmark$           | √(INPUT)     |

| B41 | CAN07_TX                       | $\checkmark$           | $\checkmark$ |

| B42 | GND                            |                        |              |

| B43 | CAN08_RX                       | $\checkmark$           | √(INPUT)     |

| B44 | CAN08_TX                       | $\checkmark$           | $\checkmark$ |

| B45 | GND                            |                        |              |

| B46 | CAN09_RX                       | $\checkmark$           | √(INPUT)     |

| B47 | CAN09_TX                       | $\checkmark$           | $\checkmark$ |

| B48 | GND                            |                        |              |

| B49 | CAN10_RX                       | $\checkmark$           | √(INPUT)     |

| B50 | CAN10_TX                       | $\checkmark$           | $\checkmark$ |

| B51 | GND                            |                        |              |

| B52 | CAN11_RX                       | $\checkmark$           | √(INPUT)     |

| B53 | CAN11_TX                       | $\checkmark$           | $\checkmark$ |

| B54 | GND                            |                        |              |

| B55 | CAN12_RX                       | $\checkmark$           | √(INPUT)     |

| B56 | CAN12_TX                       | $\checkmark$           | $\checkmark$ |

| B57 | GND                            |                        |              |

| B58 | CAN13_RX                       | $\checkmark$           | √(INPUT)     |

| B59 | CAN13_TX                       | $\checkmark$           | $\checkmark$ |

| B60 | GND                            |                        |              |

| B61 | CAN14_RX                       | $\checkmark$           | √(INPUT)     |

| B62 | CAN14_TX                       | $\checkmark$           | $\checkmark$ |

| B63 | GND                            |                        |              |

| B64 | CAN15_RX                       | $\checkmark$           | √(INPUT)     |

| B65 | CAN15_TX                       | $\checkmark$           | $\checkmark$ |

| B66 | GND                            |                        |              |

| B67 | PA15_DSPI0_SOUT                | $\checkmark$           | $\checkmark$ |

| B68 | PA13_DSPI0_SCK                 | $\checkmark$           | $\checkmark$ |

| Pin  | Pin Name /<br>Primary Function | Alternate<br>Functions | GPIO?        |

|------|--------------------------------|------------------------|--------------|

| B69  | PA14_DSPI0_SIN                 | $\checkmark$           | $\checkmark$ |

| B70  | PB09_DSPI0_CS1                 | $\checkmark$           | $\checkmark$ |

| B71  | PB10_DSPI0_CS2                 | $\checkmark$           | $\checkmark$ |

| B72  | GND                            |                        |              |

| B73  | PA06_DSPI1_SOUT                | $\checkmark$           | $\checkmark$ |

| B74  | PA08_DSPI1_SCK                 | $\checkmark$           | $\checkmark$ |

| B75  | PF15_DSPI1_SIN                 | $\checkmark$           | $\checkmark$ |

| B76  | PA07_DSPI1_CS0                 | $\checkmark$           | $\checkmark$ |

| B77  | GND                            |                        |              |

| B78  | PA11_DSPI5_SOUT                | $\checkmark$           | $\checkmark$ |

| B79  | PA09_DSPI5_SCK                 | $\checkmark$           | $\checkmark$ |

| B80  | PA10_DSPI5_SIN                 | $\checkmark$           | $\checkmark$ |

| B81  | PA12_DSPI5_CS0                 | $\checkmark$           | $\checkmark$ |

| B82  | JTAG_TCK                       |                        | $\checkmark$ |

| B83  | JTAG_TDO                       |                        | $\checkmark$ |

| B84  | JTAG_TDI                       |                        | $\checkmark$ |

| B85  | JTAG_TMS                       |                        | $\checkmark$ |

| B86  | JCOMP                          |                        |              |

| B87  | GND                            |                        |              |

| B88  | PF03_CLKOUT0                   |                        | $\checkmark$ |

| B89  | PF04_CLKOUT1                   |                        | $\checkmark$ |

| B90  | GND                            |                        |              |

| B91  | FLXR0A_RX_D                    | $\checkmark$           | $\checkmark$ |

| B92  | FLXR0A_TX_D                    | $\checkmark$           | $\checkmark$ |

| B93  | FLXR0A_TXEN#                   | $\checkmark$           | $\checkmark$ |

| B94  | GND                            |                        |              |

| B95  | FLXR0B_RX_D                    | $\checkmark$           | $\checkmark$ |

| B96  | FLXR0B_TX_D                    | $\checkmark$           | $\checkmark$ |

| B97  | FLXR0B_TXEN#                   | $\checkmark$           | $\checkmark$ |

| B98  | GND                            |                        |              |

| B99  | PB12_FXCAN2_RX                 | $\checkmark$           | $\checkmark$ |

| B100 | PB11_FXCAN2_TX                 | $\checkmark$           | $\checkmark$ |

| B101 | GND                            |                        |              |

| B102 | PB14_FXCAN3_RX                 | $\checkmark$           | $\checkmark$ |

| B103 | PB13_FXCAN3_TX                 | $\checkmark$           | $\checkmark$ |

| B104 | GND                            |                        |              |

|      |                                |                        |              |

|      | Primary Function | Functions    | GPIO?        |

|------|------------------|--------------|--------------|

| B105 | LIN0_RX          |              | √(INPUT)     |

| B106 | LIN0_TX          | $\checkmark$ | $\checkmark$ |

| B107 | GND              |              |              |

| B108 | LIN1_RX          | $\checkmark$ | √(INPUT)     |

| B109 | LIN1_TX          | $\checkmark$ | $\checkmark$ |

| B110 | GND              |              |              |

| B111 | LIN2_RX          | $\checkmark$ | √(INPUT)     |

| B112 | LIN2_TX          | $\checkmark$ | $\checkmark$ |

| B113 | GND              |              |              |

| B114 | LIN3_RX          |              | √(INPUT)     |

| B115 | LIN3_TX          | $\checkmark$ | $\checkmark$ |

| B116 | GND              |              |              |

| B117 | PCIE1_CLKC_N     |              |              |

| B118 | PCIE1_CLKC_P     |              |              |

| B119 | GND              |              |              |

| B120 | PCIE0_CLKC_N     |              |              |

| B121 | PCIE0_CLKC_P     |              |              |

| B122 | GND              |              |              |

| B123 | PMIC_FSOUT#      |              |              |

| B124 | PMIC_FIN         |              |              |

| B125 | VDD_OTP          |              |              |

| B126 | PMIC_PWRON1      |              |              |

| B127 | PMIC_PSYNC       |              |              |

| B128 | PMIC_FOUT/AMUX   |              |              |

| B129 | GND              |              |              |

| B130 | PC09_UART0_TX    | $\checkmark$ | $\checkmark$ |

| B131 | PC10_UART0_RX    | $\checkmark$ | $\checkmark$ |

| B132 | GND              |              |              |

| B133 | PB01_I2C0_SCL    | $\checkmark$ | $\checkmark$ |

| B134 | PB00_I2C0_SDA    | $\checkmark$ | $\checkmark$ |

| B135 | PB03_I2C1_SCL    | $\checkmark$ | $\checkmark$ |

| B136 | PB04_I2C1_SDA    | $\checkmark$ | $\checkmark$ |

| B137 | PB05_I2C2_SCL    | $\checkmark$ | $\checkmark$ |

| B138 | PB06_I2C2_SDA    | $\checkmark$ | $\checkmark$ |

| B139 | GND              |              |              |

| B140 | GND              |              |              |

| Pin  | Pin Name /<br>Primary Function | Alternate<br>Functions | GPIO? |

|------|--------------------------------|------------------------|-------|

| B141 | GND                            |                        |       |

| B142 | GND                            |                        |       |

| B143 | GND                            |                        |       |

| B144 | GND                            |                        |       |

| B145 | GND                            |                        |       |

| B146 | GND                            |                        |       |

| B147 | GND                            |                        |       |

| B148 | +VIN                           |                        |       |

| B149 | +VIN                           |                        |       |

| B150 | +VIN                           |                        |       |

| B151 | +VIN                           |                        |       |

| B152 | +VIN                           |                        |       |

| B153 | +VIN                           |                        |       |

| B154 | +VIN                           |                        |       |

| B155 | +VIN                           |                        |       |

| B156 | +VIN                           |                        |       |

Table 8 Module connector: bottom pins

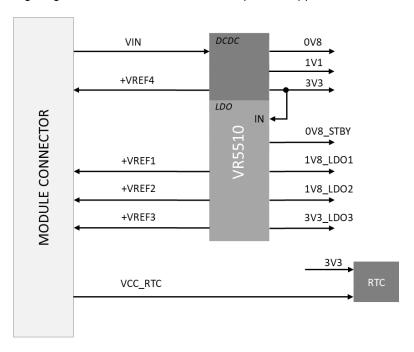

### 4.2 Power Structure

The MPX-S32G274A module is supplied by a single 9-30V supply. Onboard voltages are generated by the PMIC VR5510.

For RTC backup buffering an additional supply from the carrier is necessary.

The module itself does not provide any supply voltage to the carrier but it has some reference voltages that show the voltage level of the respective interface on the module. If necessary, the carrier must track the reference voltages and generate a copy which can carry higher loads.

The following diagram shows the structure of the power supplies:

Figure 4-1 Power supplies: structure

The following table shows the internal connections:

| Module Connector         |          |           |                                                    |  |  |  |  |  |  |

|--------------------------|----------|-----------|----------------------------------------------------|--|--|--|--|--|--|

| Pin                      | Signal   | I/O Range | Description                                        |  |  |  |  |  |  |

| T146-T154 /<br>B148-B156 | VIN      | 9-30V     | Module supply input                                |  |  |  |  |  |  |

| T117                     | +VREF1   | 1.8V      | Reference voltage output                           |  |  |  |  |  |  |

| T118                     | +VREF2   | 1.8V      | Reference voltage output                           |  |  |  |  |  |  |

| T119                     | +VREF3   | 3.3V      | Reference voltage output                           |  |  |  |  |  |  |

| T120                     | +VREF4   | 3.3V      | Reference voltage output                           |  |  |  |  |  |  |

| T133                     | VCC_RTC  | 0.9V-5.5V | Optional backup supply                             |  |  |  |  |  |  |

| T134                     | +3V3_EXT | 3.3V      | Optional boot EEPROM pro-<br>gramming supply input |  |  |  |  |  |  |

| B125                     | VDD_OTP  | N/A       | Do not connect                                     |  |  |  |  |  |  |

Table 9 Module connector: power pin assignments

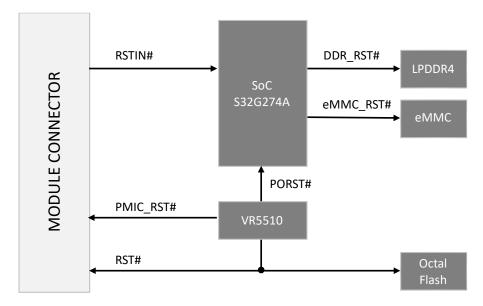

## 4.3 Reset Structure

Figure 4-2 Reset Structure

The reset structure of the MPX-S32G274A module is shown in Figure 4-2. The board resets are controlled by the system power management chip (PMIC) VR5510.

When the onboard voltages of the module are within their limits, the power good signal in combination with the RSTIN# signal will release the PORST# of the SoC. The PMIC\_RST# controls both the SoC and peripheral devices. PMIC\_RST# and RST# are identical signals. The only difference is that RST# could be disconnected by a zero-ohm resistor.

The S32G274A provides dedicated reset signals for eMMC and LPDDR4 memories.

| Signal Name | Function                   | Туре                                       |

|-------------|----------------------------|--------------------------------------------|

| RSTIN#      | System Global Reset Input  | 100R series resistance / 10nF / 4k7 Pullup |

| RST#        | System Global Reset Output | Open Drain                                 |

| PMIC_RST#   | System Global Reset Output | Open Drain                                 |

| PORST#      | Power-On Reset for SoC     |                                            |

| DDR_RST#    | Reset for LPDDR Memory     |                                            |

| EMMC_RST#   | Reset for eMMC Memory      |                                            |

Table 4-3 Reset signal overview

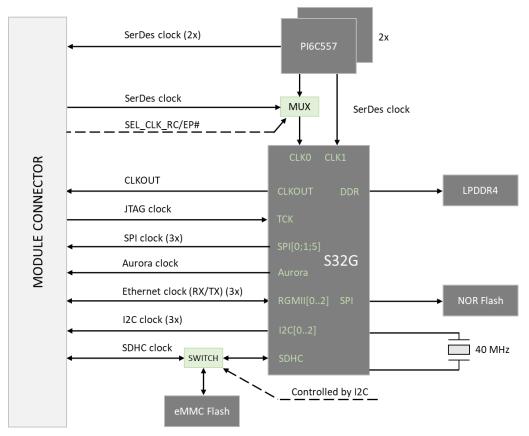

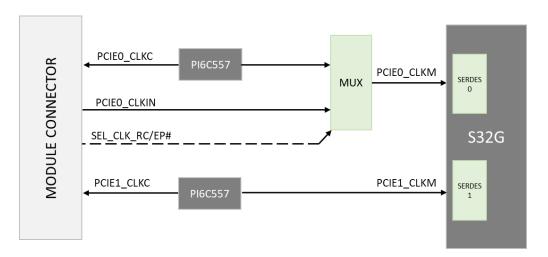

## 4.4 Clock Structure

Figure 4-3 Clock Structure

The S32G274A offers two SerDes channels with four lanes in total which can be configured as PCIe or SGMII. In order to be compliant with the NXP documentation they are referred to as "PCIE0" and "PCIE1".

Each SerDes channel requires a clock which can be configured as 100MHz or 125MHz clock depending on PCIe or SGMII use.

| J12 | (PI6C557) | 57) S32G274A "PCIE0" channel |      |             |           |                     |             |

|-----|-----------|------------------------------|------|-------------|-----------|---------------------|-------------|

| Pin | Signal    |                              | Pin  | Signal      | I/O Range | Signal conditioning | Frequency   |

| 15  | CLK0+     | $\rightarrow$                | AB15 | PCIE0_CLK_P | HCSL      | SR: 33R<br>PD: 49R9 | 100/125 MHz |

| 14  | CLK0-     | $\rightarrow$                | AC15 | PCIE0_CLK_N | HCSL      | SR: 33R<br>PD: 49R9 | 100/125 MHz |

| J12 | (PI6C557) |               |      | М            | ctor      |                     |             |

|-----|-----------|---------------|------|--------------|-----------|---------------------|-------------|

| Pin | Signal    |               | Pin  | Signal       | I/O Range | Signal conditioning | Frequency   |

| 11  | CLK1+     | $\rightarrow$ | B121 | PCIE0_CLKC_P | HCSL      | SR: 33R<br>PD: 49R9 | 100/125 MHz |

| 10  | CLK1-     | $\rightarrow$ | B120 | PCIE0_CLKC_N | HCSL      | SR: 33R<br>PD: 49R9 | 100/125 MHz |

Table 10 PCIE0 clock: pin assignments

Channel 0 can also be configured as a PCIe Endpoint. In this case the SoC can be fed with an external clock from the carrier:

| \$   | 532G274A    |          |      | Мо            | etor      |                     |           |

|------|-------------|----------|------|---------------|-----------|---------------------|-----------|

| Ball | Signal      |          | Pin  | Signal        | I/O Range | Signal conditioning | Frequency |

| AB15 | PCIE0_CLK_P | <b>←</b> | T123 | PCIE0_CLKIN_P | HCSL      |                     | 100 MHz   |

| AC15 | PCIE0_CLK_N | <b>←</b> | T122 | PCIE0_CLKIN_N | HCSL      |                     | 100 MHz   |

Table 11 PCIe clock for endpoint configuration

#### Channel 1 is fed from J16:

| J16 | PI6C557) Module Connector |               |      |              |           |                     |             |

|-----|---------------------------|---------------|------|--------------|-----------|---------------------|-------------|

| Pin | Signal                    |               | Pin  | Signal       | I/O Range | Signal conditioning | Frequency   |

| 15  | CLK0+                     | $\rightarrow$ | B121 | PCIE1_CLKC_P | HCSL      | SR: 33R<br>PD: 49R9 | 100/125 MHz |

| 14  | CLK0-                     | $\rightarrow$ | B120 | PCIE1_CLKC_N | HCSL      | SR: 33R<br>PD: 49R9 | 100/125 MHz |

| J16 | (PI6C557) |               | Module Connector |             |           |                     |             |

|-----|-----------|---------------|------------------|-------------|-----------|---------------------|-------------|

| Pin | Signal    |               | Pin              | Signal      | I/O Range | Signal conditioning | Frequency   |

| 11  | CLK1+     | $\rightarrow$ | AB16             | PCIE1_CLK_P | HCSL      | SR: 33R<br>PD: 49R9 | 100/125 MHz |

| 10  | CLK1-     | $\rightarrow$ | AC16             | PCIE1_CLK_N | HCSL      | SR: 33R<br>PD: 49R9 | 100/125 MHz |

Table 12 PCIE1 clock: pin assignments

The following table shows the available clocks configured as primary interface on the MPX-S32G274A:

| S32G274A |                   |               | Module Connector |                   |           |                     |           |  |

|----------|-------------------|---------------|------------------|-------------------|-----------|---------------------|-----------|--|

| Ball     | Signal            |               | Pin              | Signal            | I/O Range | Signal conditioning | Frequency |  |

| E19      | SD0_CLK           | $\rightarrow$ | T2               | SD_CLK            | +VREF3    | SR: 22R             | t.b.d     |  |

| U12      | DSPI0_SCK         | $\rightarrow$ | B68              | PA13_DSPI0_SCK    | +VREF3    |                     | t.b.d     |  |

| U10      | DSPI1_SCK         | $\rightarrow$ | B74              | PA08_DSPI1_SCK    | +VREF3    |                     | t.b.d     |  |

| B8       | DSPI5_SCK         | $\rightarrow$ | B79              | PA09_DSPI5_SCK    | +VREF3    |                     | t.b.d     |  |

| E7       | I2C0_SCL          | $\rightarrow$ | B133             | PB01_I2C0_SCL     | +VREF3    | PU: 2k7             | 400 kHz   |  |

| C6       | I2C1_SCL          | $\rightarrow$ | B135             | PB03_I2C1_SCL     | +VREF3    | PU: 4k7             | 400 kHz   |  |

| A6       | I2C2_SCL          | $\rightarrow$ | B137             | PB05_I2C2_SCL     | +VREF3    | PU: 4k7             | 400 kHz   |  |

| AC13     | CLKOUT_P          | $\rightarrow$ | T82              | CLK_OUT_P         | +VREF1    | SR: 0R              |           |  |

| AB13     | CLKOUT_N          | $\rightarrow$ | T81              | CLK_OUT_N         | +VREF1    | SR: 0R              |           |  |

| AC11     | AUR_CLK_P         | <b>←</b>      | T97              | AUR_CLK_P         | +VREF1    |                     | t.b.d.    |  |

| AB11     | AUR_CLK_N         | ←             | T96              | AUR_CLK_N         | +VREF1    |                     | t.b.d.    |  |

| W9       | тск               | ←             | B82              | JTAG_TCK          | +VREF3    | PD: 10k             | t.b.d.    |  |

| V20      | RGMII0_TX_<br>CLK | $\rightarrow$ | T67              | RGMII0_TX_<br>CLK | +VREF1    | SR: 10R             | 125 MHz   |  |

| V21      | RGMII0_RX_<br>CLK | <b>←</b>      | T59              | RGMII0_RX_<br>CLK | +VREF1    | SR: 10R             | 125 MHz   |  |

| Y21      | RGMII0_MDC        | $\rightarrow$ | T50              | RGMII0_MDC        | +VREF1    | SR: 10R             | < 10 MHz. |  |

| P20      | RGMII1_TX_<br>CLK | $\rightarrow$ | T48              | RGMII1_TX_<br>CLK | +VREF1    | SR: 10R             | 125 MHz   |  |

| R21      | RGMII1_RX_<br>CLK | <b>←</b>      | T40              | RGMII1_RX_<br>CLK | +VREF1    | SR: 10R             | 125 MHz   |  |

| V23      | RGMII1_MDC        | $\rightarrow$ | T31              | RGMII1_MDC        | +VREF1    | SR: 10R             | < 10 MHz  |  |

| N19      | RGMII2_TX_<br>CLK | $\rightarrow$ | T29              | RGMII2_TX_<br>CLK | +VREF2    | SR: 10R             | 125 MHz   |  |

| P21      | RGMII2_RX_<br>CLK | <b>←</b>      | T21              | RGMII2_RX_<br>CLK | +VREF2    | SR: 10R             | 125 MHz   |  |

| M19      | RGMII2_MDC        | $\rightarrow$ | T12              | RGMII2_MDC        | +VREF2    | SR: 10R             | < 10 MHz  |  |

Table 13 Clock: pin assignments

# 4.5 Boot Mode Configuration

The MPX-S32G274A module offers several different boot modes to choose from. The settings can be done via the electronic DIP switch J8 on the module and two signals on the module connector in case the FUSE\_SEL fuse is <u>not</u> blown.

The S32G274A can retrieve the boot configuration (abbreviated: BOOT\_CFG) either from fuses or from a serial EEPROM. This latter mode is called "Serial RCON" mode. "Parallel RCON" mode is not supported by the MPX-S32G274A module.

FUSE SEL = 0

| BOOTMOD0<br>(ball W10) | BOOTMOD1<br>(ball W11) | Ethernet boot config | <b>Boot Mode</b> |

|------------------------|------------------------|----------------------|------------------|

| 0                      | 0                      | No Ethernet          | Serial Boot      |

| 0                      | 1                      | SGMII                | Serial Boot      |

| 1                      | 0                      |                      | RCON             |

| 1                      | 1                      |                      | Reserved         |

Table 14 Boot mode settings (no fuse)

FUSE SEL = 1

| BOOTMOD0<br>(ball W10) | BOOTMOD1<br>(ball W11) | Ethernet boot config | <b>Boot Mode</b> |

|------------------------|------------------------|----------------------|------------------|

| 0                      | 0                      |                      | Fuses            |

| 0                      | 1                      |                      | ruses            |

| 1                      | 0                      |                      | Serial Boot      |

| 1                      | 1                      |                      | Reserved         |

Table 15 Boot mode settings (fuses)

In Serial RCON mode the BOOT\_CFG bits are mapped to the EEPROM.

BOOT\_CFG1[7:5] configures the boot devices:

| BOOT_CFG1[7:5] | Boot Source  | Description                                | Boot<br>Location |

|----------------|--------------|--------------------------------------------|------------------|

| 000            | QuadSPI Boot | Quad/Hyper/Octal Flash (see BOOT_CFG[4:2]) | Module           |

| 010            | SD Boot      | SD Card                                    | Carrier          |

| 011            | eMMC Boot    | eMMC                                       | Module           |

Table 16 Boot devices

## 4.6 LEDs

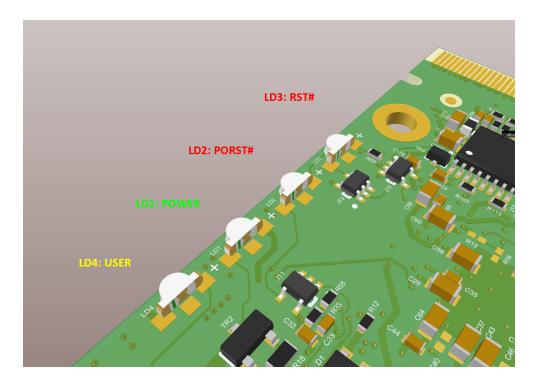

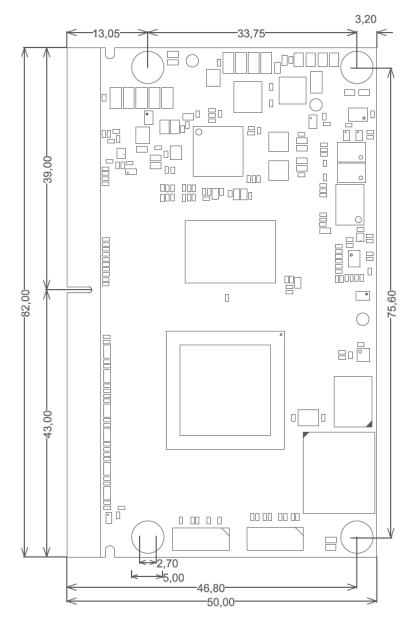

There are four LEDs on the bottom side of the MPX-S32G274A module. The side-looker LEDs are placed near the edge of the PCB.

Figure 4-4 LEDs

| Reference | Colour     | Function |                                                            |  |

|-----------|------------|----------|------------------------------------------------------------|--|

| LD1       | Green      | LED ON:  | Power-up sequence of the module is finished, power is good |  |

| LDT       | Green      | LED OFF: | Power fail                                                 |  |

| LD2       | Red        | LED ON:  | SoC Power-on-reset is active                               |  |

| LUZ       | Kea        | LED OFF: | Reset is inactive                                          |  |

| LD3       | Red        | LED ON:  | Peripheral reset is active                                 |  |

| LD3       | Red        | LED OFF: | Reset is inactive                                          |  |

| LD4       | Vollow     | LED ON:  | User defined function                                      |  |

| LD4       | LD4 Yellow | LED OFF: | User defined function                                      |  |

Table 17 LED: pin description

## 4.7 RTC

The Real-Time Clock (RTC) is implemented with an NXP PCF85263ATL chip:

- I<sup>2</sup>C clock frequency up to 400 kHz

- Operating temperature -40°C to 85°C

- Slave address according to Table 29

The RTC is supplied by 3.3V (reference voltage: +VREF4). Backup voltage is optional and needs to be provided from the carrier if buffering is desired. The following table shows the internal connection:

| Module Connector |         |             |                                                |  |  |  |

|------------------|---------|-------------|------------------------------------------------|--|--|--|

| Pin              | Signal  | I/O Range   | Description                                    |  |  |  |

| T133             | VCC_RTC | 0.9V - 5.5V | Battery backup voltage provided by the carrier |  |  |  |

Table 18 RTC: backup voltage

The RTC's interrupt output is connected to the GPIO Expander:

|     | GPIO Expander |   | PCF85263. |        |              |                     |

|-----|---------------|---|-----------|--------|--------------|---------------------|

| Pin | Signal        |   | Pin       | Signal | I/O<br>Range | Signal conditioning |

| 8   | RTC_IRQA#     | ← | 9         | INTA#  | +VREF3       | PU: 4k7             |

| 7   | RTC_IRQB#     | ← | 4         | INTB#  | +VREF3       | PU: 4k7             |

Table 19 RTC: IRQs

# 4.8 Temperature sensor

The S32G274A has an integrated temperature diode which is connected to a TMP451 temperature sensor from Texas Instruments.

- I<sup>2</sup>C clock frequency up to 400 kHz

- Operating temperature -40°C to 125°C

- Slave address according to Table 29

- Local temperature monitoring (TMP451's internal temperature)

- Remote temperature monitoring (S32G274A's temperature diode)

- Two interrupts for adjusting two temperature thresholds

|                                                | Ambient: 0°C / +70°C | Ambient: -40°C / +125°C |

|------------------------------------------------|----------------------|-------------------------|

| Local Temperature (of the sensor itself)       | Max. ± 1°C           | Max. ± 2°C              |

| Remote Temperature (of the SoC internal diode) | Max. ± 1°C           | Max. ± 4°C              |

Figure 4-5 Temperature sensor: accuracy

The temperature sensor provides two interrupts which are connected to the GPIO Expander:

| (   | GPIO Expander | TMP451 |     |               |           |                     |

|-----|---------------|--------|-----|---------------|-----------|---------------------|

| Pin | Signal        |        | Pin | Signal        | I/O Range | Signal conditioning |

| 12  | THERM_ALERT#  | ←      | 6   | ALERT#/THERM2 | +VREF3    | PU: 4k7             |

| 11  | THERM_FAULT#  | ←      | 4   | THERM#        | +VREF3    | PU: 4k7             |

Table 20 Temperature sensor: IRQs

# 4.9 **GPIO Expander**

The scope of functions on the S32G274A is extended by a GPIO expander FXL6408:

- I<sup>2</sup>C clock frequency up to 400 kHz

- Slave address according to Table 29

- One interrupt out signaling pin state changes

It has 8 GPIOs which are used as follows:

| GF  | PIO Expander |              |     |     |              |                     |

|-----|--------------|--------------|-----|-----|--------------|---------------------|

| Pin | Signal       |              |     | Pin | Signal       | Signal conditioning |

| 12  | GPIO0        | ←            | J19 | 6   | THERM_ALERT# | PU: 10k             |

| 11  | GPIO1        | ←            | J19 | 4   | THERM_FAULT# | PU: 10k             |

| 8   | GPIO2        | ←            | J21 | 9   | RTC_IRQA#    | PU: 10k             |

| 7   | GPIO3        | ←            | J21 | 4   | RTC_IRQB#    | PU: 10k             |

| 6   | GPIO4        | $\leftarrow$ | LD4 |     | USER_LED     | PU: 10k             |

| 5   | GPIO5        | ←            |     |     | HW_REV2      |                     |

| 4   | GPIO6        | ←            |     |     | HW_REV1      | See<br>Table 22     |

| 3   | GPIO7        | ←            |     |     | HW_REV0      |                     |

Table 21 GPIO Expander: Pin description

| HW_REV2 | HW_REV1 | HW_REV0 | Description         |

|---------|---------|---------|---------------------|

| 0       | 0       | 0       | Hardware Revision 1 |

| 0       | 0       | 1       | Hardware Revision 2 |

| 0       | 1       | 0       | Hardware Revision 3 |

| 0       | 1       | 1       | Hardware Revision 4 |

| 1       | 0       | 0       | Hardware Revision 5 |

| 1       | 0       | 1       | Hardware Revision 6 |

| 1       | 1       | 0       | Hardware Revision 7 |

| 1       | 1       | 1       | Hardware Revision 8 |

Table 22 GPIO Expander: Hardware Revision

| :    | S32G274A |   |     | GPIO Expander |                     |

|------|----------|---|-----|---------------|---------------------|

| Ball | Signal   |   | Pin | Signal        | Signal conditioning |

| Y7   | PC13     | ← | 1   | EXPD_IRQ#     | PU: 10k             |

Table 23 GPIO Expander: IRQ

#### 4.10 **Serial Boot EEPROM (RCON)**

In chapter 4.5 the boot modes were described. Two EEPROMs are installed on the module to store the settings for Serial RCON mode. Serial RCON mode always uses I2C0 on address 0x50 to load the board configuration.

The second EEPROM is accessible on address 0x56.

The addresses of the two EEPROMs can be swapped, thus each EEPROM can be used to load the board configuration. Swapping is achieved with the RCW\_SEL# signal from the carrier.

According to Table 16 more than two boot devices are supported. J4 is classified as primary EEPROM to store the boot configuration for SD card boot mode and it can also be write protected (see chapter 4.11). J14 is the secondary EEPROM used for any other boot configuration than SD card boot mode. J14 is not write protected. The code can be loaded by the user, stored in the EEPROM and selected via the carrier.

If the FUSE\_SEL fuse is blown the SoC will always boot from fuses (FUSE\_SEL = 1).

| FUSE_SEL | MUX_SEL# | SD / eMMC MUX (SEL_EMMC_SDHC#) | RCW_SEL# | Г        | Description                                            |

|----------|----------|--------------------------------|----------|----------|--------------------------------------------------------|

|          | 0        | SD card                        | 0        | Boot fro | m J14 configuration                                    |

| 0        | O        | 3D card                        | 1        | Boot fro | om J4 configuration                                    |

| V        | 1        | DIP Switch: • SD-Card          | 0        | Boot fro | m J14 configuration                                    |

|          | ,        | • eMMC                         | 1        | Boot fro | om J4 configuration                                    |

|          | 0        | SD card                        | v        | ES<br>ES | SD-Card                                                |

| 1        | 1        | DIP Switch: • SD-Card • eMMC   | X        | FUSES    | <ul><li>SD-Card</li><li>eMMC</li><li>SPI NOR</li></ul> |

Table 24 Boot configuration

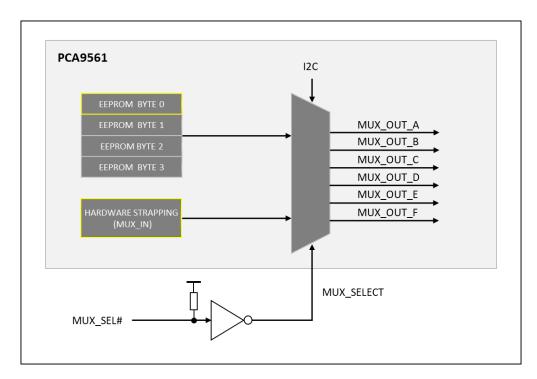

## 4.11 Electronic DIP Switch

The electronic DIP switch replaces mechanical DIP switches which can be serviced by a human operator only. The electronic DIP switch is accessed via I2C interface instead (slave address according to Table 29) and provides six persistent output signals to configure the module.

Figure 4-6 Electronic DIP Switch: Structure

At power up the values at MUX\_OUT\_x pins are either loaded from EEPROM Byte0 or MUX\_IN hardware strapping inputs depending on the MUX\_SELECT input pin of the PCA9561.

| MUX_SEL#    | MUX_SELECT |                         |

|-------------|------------|-------------------------|

| 1 (DEFAULT) | 0          | MUX_OUT = EEPROM BYTE 0 |

| 0           | 1          | MUX_OUT = MUX_IN        |

Table 25 Electronic DIP Switch: MUX\_OUT after POR

Initial EEPROM programming is done during production test and can be overridden via I2C.

| DIP Switch |            |          | Module Connector |          |           |                     |  |  |  |  |

|------------|------------|----------|------------------|----------|-----------|---------------------|--|--|--|--|

| Pin        | Signal     |          | Pin              | Signal   | I/O Range | Signal conditioning |  |  |  |  |

| 11         | MUX_SELECT | <b>←</b> | T132             | MUX_SEL# | +3V3_EXT  | PU: 10k             |  |  |  |  |

Table 26 Electronic DIP Switch: MUX\_SELECT

| MUX<br>_OUT_ | Signal Name        | MUX<br>_IN | Description |                                                                                  |  |

|--------------|--------------------|------------|-------------|----------------------------------------------------------------------------------|--|

| А            | CLKGEN1_100M/125M# | 1          | 1           | PCIE0_CLK_P/N = 100 MHz (SoC PLL)<br>PCIE0_CLKC_P/N = 100 MHz (ST1: B120 / B121) |  |

|              |                    |            | 0           | PCIE0_CLK_P/N = 125 MHz (SoC PLL)<br>PCIE0_CLKC_P/N = 125 MHz (ST1: B120 / B121) |  |

| В            | CLKGEN2_100M/125M# | 1          | 1           | PCIE1_CLK_P/N = 100 MHz (SoC PLL)<br>PCIE1_CLKC_P/N = 100 MHz (ST1: B117 / B118) |  |

|              |                    |            | 0           | PCIE1_CLK_P/N = 125 MHz (SoC PLL)<br>PCIE1_CLKC_P/N = 125 MHz (ST1: B117 / B118) |  |

| С            | RCON_EEPROM_WP     | 1          | 1           | Serial RCON EEPROM J4 write-protected                                            |  |

|              |                    |            | 0           | Serial RCON EEPROM J4 unprotected                                                |  |

| D            | SEL_EMMC_SDHC#     | 0          | 1           | Multiplexer: eMMC selected                                                       |  |

| D            |                    |            | 0           | Multiplexer: SD card selected                                                    |  |

| E            | PA02_BOOTMOD1      | 1          | 1           | Bootmode Pin 1 (J1: W10) = 1                                                     |  |

|              |                    |            | 0           | Bootmode Pin 1 (J1: W10) = 0                                                     |  |

| F            | PA03_BOOTMOD2      | 0          | 1           | Bootmode Pin 2 (J1: W11) = 1                                                     |  |

| Г            |                    |            | 0           | Bootmode Pin 2 (J1: W11) = 0                                                     |  |

Table 27 Electronic DIP Switch: MUX\_IN / MUX\_OUT

## 4.12 Interface Description

In the following chapters the interfaces of the MPX-S32G274A <u>module</u> are described.

Due to pin multiplexing there may be limitations regarding the availability of certain interfaces. Nevertheless, different pinouts are possible.

#### 4.12.1 Definition of "Primary Interfaces"

The terms "primary", "secondary", ... do not imply any priority. The connector's pin names are derived from the primary functions defined by MicroSys.

Primary interfaces can be also be configured for other interfaces. Nevertheless, high speed interfaces are optimized in layout, signals are length and often group matched. Multiplexing information for each pin can be found in the manufacturer's datasheet, some signals are used onboard (see chapter 10.6).

#### 4.12.2 JTAG

The JTAG chain of the MPX-S32G274A includes the S32G274A processor only. The JTAG port is directly connected to the MXM module connector. The JTAG interface can also be configured as GPIO.

The pins are listed in the Appendix in chapter 10.4 and 10.5.

Some debuggers require a 10k pullup on TDI and TDO pins. These are not assembled on the module and may be provided externally for debugging.

#### **4.12.3 AURORA**

The Aurora port is a trace port consisting of 4 LVDS data pairs and a LVDS clock pair. The signals are available on the module connector as primary interface with no multiplexing options.

The pins are listed in the Appendix in chapter 10.4 and 10.5.

#### 4.12.4 ADC

The ADC converter contained in the S32G274A processor has 12 multiplexed single-ended channels. They can be accessed via the MXM module connector and do not share their pins with other interfaces.

The pins are listed in the Appendix in chapter 10.4 and 10.5.

There is no protection on any ADC line against over-voltage or wrong polarity. Refer to the S32G274A datasheet for maximum ratings.

#### 4.12.5 CAN

The S32G274A has 4 FlexCANs and 16 LLCE CANs. Due to pin multiplexing there are limitations.

The MPX-S32G274A module realizes 18 CAN ports as primary interfaces on the module connector, two FlexCANs and 16 LLCE CANs. The ports support CAN2.0 version B and CAN FD protocols at data rates up to 8Mb/s. CAN transceivers are not installed on the module.

The CAN interfaces can also be configured as GPIO.

The pins are listed in the Appendix in chapter 10.4 and 10.5.

#### 4.12.6 RGMII

The S32G274A provides MACs for three RGMII interfaces, each RGMII port has a dedicated MDIO interface.

The pins are listed in the Appendix in chapter 10.4 and 10.5.

RGMII2 is also shared with an ULPI interface for USB PHYs:

| Module<br>Connector | RGMII         | ULPI    |  |  |  |

|---------------------|---------------|---------|--|--|--|

| T15                 | RGMII2_RXD3   | USB_D7  |  |  |  |

| T16                 | RGMII2_RXD2   | USB_D6  |  |  |  |

| T17                 | RGMII2_RXD1   | USB_D5  |  |  |  |

| T18                 | RGMII2_RXD0   | USB_D4  |  |  |  |

| T20                 | RGMII2_RXDV   | USB_D3  |  |  |  |

| T21                 | RGMII2_RX_CLK | USB_D2  |  |  |  |

| T23                 | RGMII2_TXD3   | USB_D1  |  |  |  |

| T24                 | RGMII2_TXD2   | USB_D0  |  |  |  |

| T25                 | RGMII2_TXD1   | USB_NXT |  |  |  |

| T26                 | RGMII2_TXD0   | USB_STP |  |  |  |

| T28                 | RGMII2_TX_EN  | USB_DIR |  |  |  |

| T29                 | RGMII2_TX_CLK | USB_CLK |  |  |  |

Table 28 RGMII2 / ULPI pin multiplexing options

## 4.12.7 ULPI (USB)

The MPX-S32G274A does not have a USB PHY but a ULPI interface. The ULPI signals are not available as primary interface on the module connector but they are shared with RGMII signals. For more details please see chapter 4.12.6.

The ULPI interface can also be configured as GPIO.

The pins are listed in the Appendix in chapter 10.4 and 10.5.

#### 4.12.8 I2C

The MPX-S32G274A module offers five I<sup>2</sup>C busses which run at up to 400kHz.

I2C3 is not available as primary interface.

I2C4 is explicitly used for the power management chip on the module.

The pins are listed in the Appendix in chapter 10.4 and 10.5.

#### I2C0 map:

| Device           |                                           | A6 | <b>A5</b> | A4 | А3 | A2 | A1 | Α0 | R/W | Addr |

|------------------|-------------------------------------------|----|-----------|----|----|----|----|----|-----|------|

| GPIO<br>Expander | FXL6408                                   | 1  | 0         | 0  | 0  | 0  | 1  | 1  | 1/0 | 0x43 |

| Temperature      | TMP451AIDQF (slave address)               | 1  | 0         | 0  | 1  | 1  | 0  | 0  | 1/0 | 0x4C |

| Sensor           | TMP451<br>(General Call reset<br>address) | 0  | 0         | 0  | 0  | 0  | 0  | 0  | -/0 | 0x00 |

| DIP Switch       | PCA9561PW                                 | 1  | 0         | 0  | 1  | 1  | 0  | 1  | 1/0 | 0x4D |

| EEPROM           | AT24C01C-SSHM                             | 1  | 0         | 1  | 0  | 0  | 0  | 0  | 1/0 | 0x50 |

| RTC              | PCF85263ATL                               | 1  | 0         | 1  | 0  | 0  | 0  | 1  | 1/0 | 0x51 |

| EEPROM           | BR24G128NUX-3                             | 1  | 0         | 1  | 0  | 1  | 0  | 0  | 1/0 | 0x54 |

| EEPROM           | AT24C01C-SSHM                             | 1  | 0         | 1  | 0  | 1  | 1  | 0  | 1/0 | 0x56 |

Table 29 I2C0: bus map

#### I2C1 map:

| Device | <b>A</b> 6 | A5 | A4 | А3 | A2 | <b>A</b> 1 | Α0 | R/W | Addr |

|--------|------------|----|----|----|----|------------|----|-----|------|

|        | <br>-      | -  | -  | -  | -  | -          | -  | -   | -    |

Table 30 I2C1: bus map

#### I2C2 map:

| Device | A6    | A5 | A4 | А3 | A2 | A1 | Α0 | R/W | Addr |

|--------|-------|----|----|----|----|----|----|-----|------|

|        | <br>- | -  | -  | -  | -  | -  | -  | -   | -    |

Table 31 I2C2: bus map

I2C 3 is available by multiplexing functions. Primary interface is FlexCAN3.

#### I2C4 map:

| Device |                        | A6 | A5 | A4 | А3 | A2 | <b>A</b> 1 | Α0 | R/W | Addr |

|--------|------------------------|----|----|----|----|----|------------|----|-----|------|

| PMIC   | VR5510 Main logic      | 0  | 1  | 0  | 0  | 0  | 0          | 0  | 1/0 | 0x20 |

| PMIC   | VR5510 Fail-safe logic | 0  | 1  | 0  | 0  | 0  | 0          | 1  | 1/0 | 0x21 |

Table 32 I2C4: bus map

#### 4.12.9 QSPI (Flash)

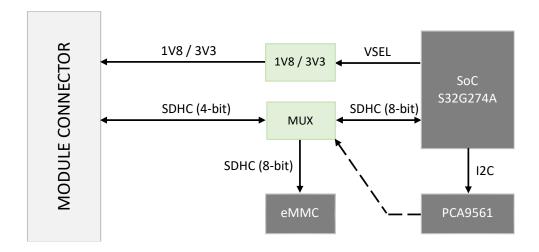

The MPX-S32G274A uses the QSPI port A to connect a serial NOR lash (8-bit bus).

The following table shows the internal connections:

|      | S32G274A      |                   | SPI NOR Flash<br>MT35XU512ABA1G12 |        |              |

|------|---------------|-------------------|-----------------------------------|--------|--------------|

| Ball | Signal        |                   | Pin                               | Signal | I/O<br>Range |

| G21  | QSPI1_A_CS0#  | $\rightarrow$     | C2                                | CS#    | 1.8V         |

| K20  | QSPI1_A_SCK   | $\rightarrow$     | B2                                | CLK    | 1.8V         |

| K23  | QSPI_A_DQS    | $\leftarrow$      | C3                                | DQS    |              |

|      |               |                   | B3, E5, C1                        | GND    |              |

| L18  | QSPI1_A_DATA0 | $\leftrightarrow$ | D3                                | D0     | 1.8V         |

| L19  | QSPI1_A_DATA1 | $\leftrightarrow$ | D2                                | D1     | 1.8V         |

| L20  | QSPI1_A_DATA2 | $\leftrightarrow$ | C4                                | D2     | 1.8V         |

| K22  | QSPI1_A_DATA3 | $\leftrightarrow$ | D4                                | D3     | 1.8V         |

| K19  | QSPI1_A_DATA4 | $\leftrightarrow$ | D5                                | D4     | 1.8V         |

| J23  | QSPI1_A_DATA5 | $\leftrightarrow$ | E3                                | D5     | 1.8V         |